# TCG PC Specific Implementation Specification

# Version 1.1 August 18, 2003

Copyright © 2003 Trusted Computing Group, Incorporated.

Copyright © 2001 Compaq Computer Corporation, Hewlett-Packard Company, IBM Corporation, Intel Corporation, Microsoft Corporation

Previously published by Trusted Computing Platform Alliance under the title: "TCPA PC Specific Implementation Specification, Version 1.00, September 09, 2001".

### **DISCLAIMERS:**

THIS SPECIFICATION IS PROVIDED "AS IS" WITH NO WARRANTIES WHATSOEVER, INCLUDING ANY WARRANTY OF MERCHANTABILITY, NONINFRINGEMENT, FITNESS FOR ANY PARTICULAR PURPOSE, OR ANY WARRANTY OTHERWISE ARISING OUT OF ANY PROPOSAL, SPECIFICATION OR SAMPLE. Without limitation, TCG disclaims all liability, including liability for infringement of any proprietary rights, relating to use of information in this specification and to the implementation of this specification, and TCG disclaims all liability for cost of procurement of substitute goods or services, lost profits, loss of use, loss of data or any incidental, consequential, direct, indirect, or special damages, whether under contract, tort, warranty or otherwise, arising in any way out of use or reliance upon this specification or any information herein.

No license, express or implied, by estoppel or otherwise, to any TCG or TCG member intellectual property rights is granted herein.

Except that a license is hereby granted by TCG to copy and reproduce this specification for internal use only.

Contact the Trusted Computing Group at www.trustedcomputinggroup.org for information on specification licensing through membership agreements.

Any marks and brands contained herein are the property of their respective owners.

# **Change History**

| Version    | Date               | Description                                                                                                                                                                                                                                                                                                                                     |  |

|------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 1.00 RC1   | August 16, 2001    | Proposed initial release candidate                                                                                                                                                                                                                                                                                                              |  |

| 1.00 RC1.1 | August 23, 2001    | Editorial Corrections.                                                                                                                                                                                                                                                                                                                          |  |

| 1.00 RC 2  | August 23, 2001    | Re-added Preface to give a location for post release comments. Change 7.2.3 EV_ACTION Event Types event: "Booting BCV Device s" Made clarifications to wording in section 8.3.2                                                                                                                                                                 |  |

| 1.00 Final | September 09, 2001 | Final Release                                                                                                                                                                                                                                                                                                                                   |  |

| 1.1        | July 16, 2003      | Moved to a TCG specification. Minor textual corrections.                                                                                                                                                                                                                                                                                        |  |

| 1.1 RC2    | July 23, 2003      | Note: Previous version released as RC1 but not labeled as such. Added flag to pre-boot PCR in the case where no measurement can be taken. Changed name of event structure and make reference to TSS spec Make clarifications and corrections to the parameter block definitions in section 8. Added ending pointer to Event Log in StatusCheck. |  |

| 1.1 RC2A   | Aug 13, 2003       | Make changes to section 8.2 to clarify flat model.  Add TPM Configuration port definition to header                                                                                                                                                                                                                                             |  |

| 1.1 RC3    | Aug 18, 2003       | Changed references back to the TCPA Main Specification. Clarifications added to TCG_StatusCheck Added Clarification to LogEventType in TCG_LogEvent Enhanced section 8.2.1 to further describe the behavior of segments. Added TPM and channel error responses. Added configuration port.                                                       |  |

# **Table of Contents**

| <ol> <li>Introd</li> </ol> | uction and Concepts                               | 6    |

|----------------------------|---------------------------------------------------|------|

| 1.1 PC                     | Architecture                                      | 6    |

| 1.2 Def                    | initions                                          | 9    |

| 1.2.1                      | BIOS Recovery Mode                                |      |

| 1.2.2                      | Core RTM (CRTM)                                   |      |

| 1.2.3                      | Central Processing Unit (CPU)                     |      |

| 1.2.4                      | Immutable                                         |      |

| 1.2.5                      | Initial Program Loader (IPL)                      | 0    |

|                            | Manufacturer                                      | ٠ ١  |

| 1.2.6                      | Manufacturer                                      | ١١ . |

| 1.2.7                      | Measurement and Measure                           |      |

| 1.2.8                      | Motherboard                                       |      |

| 1.2.9                      | Pre-Boot State                                    |      |

| 1.2.10                     | Post-Boot State                                   |      |

| 1.2.11                     | Platform                                          |      |

| 1.2.12                     | Platform Reset                                    |      |

| 1.2.13                     | System                                            |      |

| 1.2.14                     | TCPA Main Specification v1.1b                     |      |

| 1.2.15                     | TCG TSS Specification                             | . 11 |

| 1.2.16                     | Trusted Building Block (TBB)                      |      |

|                            | ncepts                                            |      |

| 1.3.1                      | Immutable                                         |      |

| 1.3.2                      | Trusted Building Block (TBB)                      |      |

| 1.3.3                      | Platform Reset Types                              |      |

| 1.3.4                      | Core RTM (CRTM)                                   |      |

| 1.3.5                      | Boot State Transition                             |      |

| 1.3.6                      | Establishing the Chain of Trust                   |      |

|                            | ity Collection & Reporting                        |      |

|                            | ncepts                                            |      |

| 2.1.1                      | Initial TBB control and Platform Reset            |      |

|                            | Transferring Control                              |      |

|                            |                                                   |      |

|                            | R Usage                                           |      |

| 2.2.1                      | PCR[0] – CRTM, POST BIOS and Embedded Option ROMs | ١٤.  |

| 2.2.2                      | PCR[1] - Motherboard Configuration                |      |

| 2.2.3                      | PCR[2] - Option ROM Code                          | . 16 |

| 2.2.4                      | PCR[3] – Option ROM Configuration and Data        |      |

| 2.2.5                      | PCR[4] - IPL Code                                 |      |

| 2.2.6                      | PCR[5] – IPL Configuration and Data               |      |

| 2.2.7                      | PCR[6] – State Transition                         |      |

| 2.2.8                      | PCR[7] – Reserved                                 |      |

|                            | rm Setup and Configuration                        |      |

|                            | -Boot ROM-based Setup                             |      |

|                            | st-Boot ROM-based Setup                           |      |

|                            | erence Partition                                  |      |

| 3.4 OS                     | Based Setup Utility                               | . 20 |

| 4. Mainte                  | enance                                            | .2   |

|                            | S Recovery Mode                                   |      |

|                            | sh Maintenance                                    |      |

| 4.2.1                      | Manufacturer Approved Environment (MAE)           |      |

| 4.2.2                      | Non-Manufacturer Approved Environment (NMAE)      |      |

|                            | Credentials                                       |      |

|                            | tform Certificate                                 |      |

|                            |                                                   |      |

|    | 5.2 Plat               | tform Conformance Certificate                               | 23 |

|----|------------------------|-------------------------------------------------------------|----|

|    |                        | thod of Verification                                        |    |

|    |                        | idation Certificate Header                                  |    |

| 6. |                        | ode, Power States, and Transitions                          |    |

|    |                        | hitecture and Definitions                                   |    |

|    | 6.2 Pro                | cedure for Transitioning the TPM from Pre-Boot to Post-Boot |    |

|    | 6.2.1                  | Extending PCR[4] – The IPL Code                             |    |

|    | 6.2.2                  | Extending PCR[5] – IPL Configuration and Data               |    |

|    | 6.2.3                  | Logging of Boot Events                                      |    |

|    | 6.2.4                  | Passing Control of the TPM from Pre-Boot to Post-Boot       |    |

|    | 6.2.5                  | Various Boot Devices and Special Treatment they may receive |    |

|    |                        | ver States, Transitions, and TPM Initialization             |    |

|    | 6.3.1                  | Definitions and Conditions during Power States              |    |

|    | 6.3.2                  | Power State Transitions                                     |    |

|    |                        | Logging                                                     |    |

|    |                        | PI Table Usage                                              |    |

|    |                        | asurement Event Log                                         |    |

|    | 7.2.1                  |                                                             |    |

|    | 7.2.2                  |                                                             |    |

| _  | 7.2.3                  | EV_ACTION Event Types                                       |    |

|    |                        | mentation                                                   |    |

|    |                        | Dication Level Interface                                    |    |

|    | 8.1.1                  | General Calling Convention                                  |    |

|    | 8.1.2                  | Return Codes                                                |    |

|    | 8.1.3                  | Parameter Block                                             |    |

|    | 8.1.4                  | TCG_StatusCheck                                             |    |

|    | 8.1.5                  | TCG_HashLogExtendEvent                                      |    |

|    | 8.1.6<br>8.1.7         | TCG_PassThroughToTPM                                        |    |

|    | 8.1. <i>1</i><br>8.1.8 | TCG_ShutdownPreBootInterface TCG_LogEvent                   |    |

|    | 8.1.9                  | TCG_LogEvent                                                |    |

|    | 8.1.10                 | TCG_TISS                                                    |    |

|    | 8.1.11                 | TCG_BIOSReserved                                            |    |

|    | 8.1.12                 | TCG_BIOSVendorReserved                                      |    |

|    |                        | V Driver Interfaces                                         |    |

|    | 8.2.1                  | Module Architectures                                        |    |

|    | 8.2.2                  | Memory Absent (MA) Driver                                   |    |

|    | 8.2.3                  | Memory Present (MP) Driver                                  |    |

|    |                        | /sical Presence                                             |    |

|    | 8.3.1                  | Physical Switch                                             |    |

|    | 8.3.2                  | Indication of Physical Presence from the CRTM               |    |

|    | 0.0.2                  | maioution of rangolour radiono nom the ortal viscosistics   |    |

# **Corrections and Comments**

Please send corrections and comments regarding this specification to:

http://www.trustedcomputinggroup.org

# 1. Introduction and Concepts

### Start of informative comment:

The Trusted Computing Group's TCPA Main Specification v1.1b (http://www.trustedcomputinggroup.org) (hereafter, referred to as the TCPA Main Specification) has been written as a platform independent document to enhance trust on computing platforms. As such, the TCPA Main Specification is general in specifying both hardware and software requirements. The goal of the TCG member companies is to ensure compatibility among implementations within each computing architecture. It is expected that companion implementation documents will be created for each architecture.

This document serves as implementation reference document for the 32-bit PC architecture. Specifically, this document defines:

- Usage of PCR registers in the Pre-Boot state through the transition to Post-Boot state.

- How the BIOS, or a component thereof, functions as the Core Root of Trust for Measurement (CRTM).

- Programmatic Interfaces to the BIOS as it performs the functions of the TCG Subsystem (TSS and access to the TPM)

- Behavior entering, during, and exiting power and initialization states.

- Guidelines for Option ROMS.

This specification is based on the *TCPA Main Specification*. The reader is expected to have an understanding of the concepts, defined functionality, and terms expressed in that document. This specification will attempt to minimize the duplication of information from that document, therefore, concepts and terms defined in the TCPA Main Specification will not be defined in this document. If there is a conflict in interpretation between this and the TCPA Main Specification, the concept or functional description as defined in the TCPA Main Specification will take precedence.

This specification also references the following specifications. The reader is expected to be familiar with the concepts and terminology contained in each where relevant:

- Plug and Play BIOS Specification Version 1.0A

- Advanced Configuration and Power Interface Specification; Revision 2.0 July 27, 2000

- BIOS Boot Specification; Version 1.01 January 11, 1996

- Boot Integrity Services Application Programming Interface; Version 1.0

- System Management BIOS Reference Specification

- "El Torito" Bootable CD-ROM Format Specification; Version 1.0; January 25, 1995

- Preboot Execution Environment (PXE) Specification; Version 2.1

- PARTIES (Protected Area Run Time Interface Extension Services) Working Draft;T13 D1367; Revision 3 September 30, 2000.

# End of informative comment.

# 1.1 PC Architecture

# Start of informative comment:

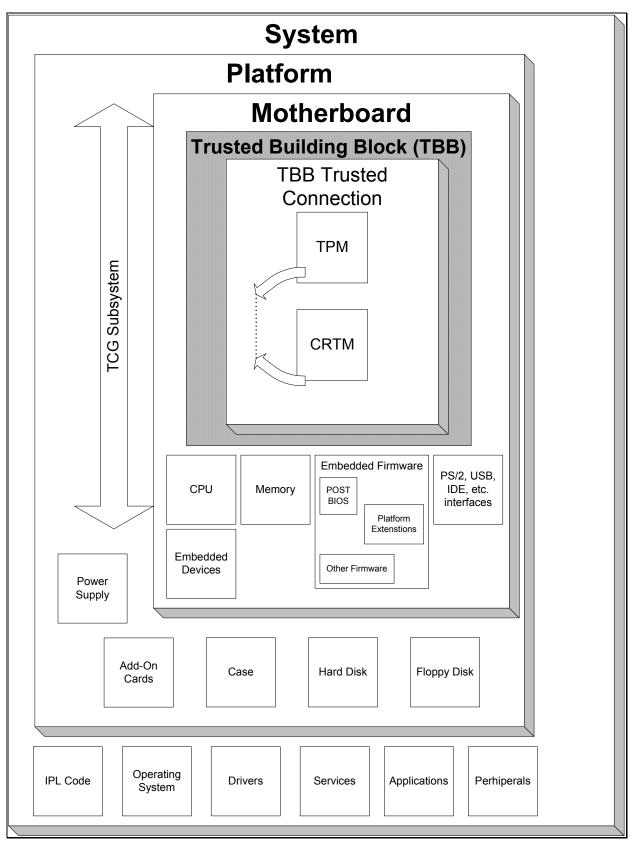

The concepts and descriptions of the PC architecture are described below in both the diagram and the descriptions. While the diagram infers physical connections, the connections and associations between the components are logical.

■ Figure 1-1 Components of the PC

# 1.2 Definitions

# Start of informative comment:

[These are in alphabetical order because of some cyclic definition dependencies.]

End of informative comment.

# 1.2.1 BIOS Recovery Mode

# Start of informative comment:

This is a failure-recovery mode of the BIOS that is invoked by the BIOS Boot Block typically when the main BIOS is corrupt. See section 4.1 BIOS Recovery Mode.

End of informative comment.

# 1.2.2 Core RTM (CRTM)

# Start of informative comment:

The executable component of the RTM that gains control of the Platform upon a Platform Reset. See more detailed description of this in Section 1.3.4 Core RTM (CRTM).

End of informative comment.

# 1.2.3 Central Processing Unit (CPU)

# Start of informative comment:

The computing engine of the Platform. Multiple CPUs may be contained on a single Platform but, for the purposes of this specification, are treated as a single unit. In a multiple CPU Platform, each CPU must perform reset and initialization as defined in Platform Reset. Platforms containing multiple CPUs are assumed to load and execute the same Operating System. For the purpose of the remainder of this specification, the term CPU will refer to all CPUs on the Platform.

End of informative comment.

# 1.2.4 Immutable

# Start of informative comment:

See Section 1.3.1 Immutable.

End of informative comment.

# 1.2.5 Initial Program Loader (IPL)

# Start of informative comment:

This is the code that executes during the Post-Boot state. The purpose of this code is to load the Post-Boot environment.

# 1.2.6 Manufacturer

# Start of informative comment:

The entity that makes and attests to the validity of a component. In this specification, unless otherwise noted, this refers to the maker of the TBB. Unless otherwise stated, this refers to the Manufacturer of the Motherboard.

### End of informative comment.

# 1.2.7 Measurement and Measure

### Start of informative comment:

These terms mean: perform hash, log and extend to the appropriate PCR(s).

End of informative comment.

# 1.2.8 Motherboard

### Start of informative comment:

An entity that is supplied by the Manufacturer which is comprised of the TBB and other components physically or logically attached and supplied by the Manufacturer.

End of informative comment.

# 1.2.9 Pre-Boot State

# Start of informative comment:

The state of the system prior to the invocation of the INT 19h or its equivalent.

End of informative comment.

# 1.2.10 Post-Boot State

# Start of informative comment:

The state of the system after the invocation of the first INT 19h or its equivalent. This may include OS, PARTIES, diagnostics, etc.

End of informative comment.

# 1.2.11 Platform

# Start of informative comment:

The entity that presents and receives information to and from the user. The Platform is composed of the Motherboard to which the CPU and primary peripheral devices are attached<sup>1</sup>, the CPU(s), all BIOSes, the TPM, and peripherals attached to the main board.

<sup>&</sup>lt;sup>1</sup> Primary peripheral device refers to devices which directly attach to an directly interact with the CPU. Examples are PCI cards, LPC components, USB Host controller and root hub, attached serial and parallel ports, etc. Examples of devices not included in this class are USB and IEEE 1394 devices.

# 1.2.12 Platform Reset

### Start of informative comment:

This can be caused by several events, including those in the following non-exclusive list: Initial Power-On, Activation of a hardware reset line (i.e., PCI\_Reset) including activation of the TPM\_Init signal, initiated by the OS to begin a new boot session, and initiated by the CPU during certain unrecoverable fault conditions. The Platform is to have a consistent behavior, from a trust perspective, regardless of the type of reset performed.

# End of informative comment.

The event that causes the components of the Platform to enter their reset condition including the TPM (caused by a TPM\_Init). Upon a Platform Reset, the CPU MUST begin execution at the CRTM. This event MUST cause a PCI\_Reset. Unless otherwise stated, the result of a Platform Reset MUST cause the equivalent of transitioning the motherboard from the S5 state (i.e., It may not cause a transition from S3.)

# 1.2.13 System

### Start of informative comment:

This includes the Platform and all the Post-Boot components that comprise the entire entity that performs actions for, or acts on behalf of, the user.

### End of informative comment.

# 1.2.14 TCPA Main Specification v1.1b

# Start of informative comment:

Refers to the TCPA Main Specification v1.1b as released by the Trusted Computing Group. This "TCG PC Specific Implementation Specification" is based on the TCPA Main Specification v1.1b.

# End of informative comment.

# 1.2.15 TCG TSS Specification

# Start of informative comment:

Refers to the TCG TSS Specification version 1.1 as released.

End of informative comment.

# 1.2.16 Trusted Building Block (TBB)

### Start of informative comment:

The combination of the CRTM, TPM, connection of the CRTM to the motherboard, and the connection of the TPM to the motherboard. See section 1.3.2 Trusted Building Block (TBB).

# 1.3 Concepts

# 1.3.1 Immutable

In this specification immutable means that in order to maintain trust in the Platform, the replacement or modification of code or data MUST be performed by a Platform manufacturer-approved agent and method. This allows a manufacturer to establish an upgrade method for the portion of the Platform which is the CRTM with consideration of the security properties of the Platform's Protection Profile.

# 1.3.2 Trusted Building Block (TBB)

The combination of the CRTM, TPM, connection of the CRTM to the motherboard, and the connection of the TPM to the motherboard. The connection of the CRTM to the TPM is done through transitive trust of the CRTM connection and the TPM connection.

Since the CRTM and the TPM are the only trusted components of the Motherboard and since indication of physical presence requires a trusted mechanism to be activated by the platform owner, the indication of physical presence MUST be contained within the TBB.

# 1.3.3 Platform Reset Types

# Start of informative comment:

A Cold Boot Platform Reset occurs when transitioning the Platform from a full Power-Off state in which no OS specific state or status is preserved on the Platform except for that which is contained on any OS load device to a Power-On state. This excludes returning from various power or suspend states which can occur after the Cold Boot Reset from an OS present state.

A Hardware Platform Reset occurs when a signal activates the reset signal of all Platform components. This may be a user initiated event or a software initiated event trigged by a command to a hardware component which asserts the reset line.

A Warm Boot Platform Reset occurs when software (often caused by a user keyboard input but may be software induced) causes a Platform Reset.

### End of informative comment.

For all types of Platform Resets the CPU SHALL begin executing code with the CRTM's Platform initialization code. The Platform MUST perform a Platform Reset. No System component SHALL block the PCI\_Reset signal to any of the System components.

# 1.3.4 Core RTM (CRTM)

The Core Root of Trust for Measurement (CRTM) MUST be an immutable portion of the Platform's initialization code that executes upon a Platform Reset. The Platform's execution MUST begin at the CRTM upon any Platform Reset.

The trust in the Platform is based on this component. The trust in all measurements is based on the integrity of this component.

Currently, in a PC, there are at least two types of CRTM architectures:

CRTM is the BIOS Boot Block.

# Start of informative comment:

In this architecture the BIOS is composed of a BIOS Boot Block and a POST BIOS. Each of these are independent components and each can be updated independent of the other. In this

architecture, the BIOS Boot Block is the CRTM while the POST BIOS is not, but is a measured component of Chain of Trust.

### End of informative comment.

The Manufacturer MUST control the update, modification, and maintenance of the BIOS Boot Block component, while either the Manufacturer or a 3<sup>rd</sup> party supplier may update, modify, or maintain the POST BIOS component. If there are multiple execution points for the BIOS Boot Block, they must all be within the CRTM.

CRTM is the entire BIOS

# Start of informative comment:

In this architecture the BIOS is composed of a single atomic entity. The entire BIOS is updated, modified or maintained as a single component. In this architecture, the entire BIOS is the CRTM.

# End of informative comment.

The Manufacturer MUST control the update, modification, and maintenance of the entire BIOS

# 1.3.5 Boot State Transition

The transition between Pre-Boot and Post-Boot states is the first invocation of INT 19h or equivalent.

# 1.3.6 Establishing the Chain of Trust

# 1.3.6.1 **Bindings**

# 1.3.6.1.1 Bindings between an Endorsement Key, a TPM, and a Platform.

The relationship between the Endorsement Key, a TPM, and a Platform is described in Section 2.2 of the TCPA Main Specification.

# 1.3.6.1.2 Binding Methods.

### Start of informative comment:

The method of binding the TPM to the Motherboard is an architectural and design decision made by the respective manufacturer and is not specified here. There are two types of binding: Physical and Logical. Physical binding relies on hardware techniques while Logical binding relies on cryptographic techniques. The nature and strength of each method is defined by the TPM's or the Platform's Protection Profile.

# Examples:

- 1. The TPM is a physical chip soldered to the Platform. Here the Endorsement Key is physically bound to the TPM (it's inside it) and the TPM is physically bound to the Platform by the solder. The required strength of each binding is determined by the Protection Profile.

- 2. The TPM is a SmartCard with the Endorsement Key inside. The SmartCard is on a "common" bus (e.g., USB). The Endorsement Key, as in example 1, is physically bound to the TPM but the TPM now must be bound to the Platform via some cryptographic method. An example is a common shared secret within both the Platform and the SmartCard would enforce each to function only with the appropriate component.

# 2. Integrity Collection & Reporting

# 2.1 Concepts

# 2.1.1 Initial TBB control and Platform Reset

Upon Platform Reset the CRTM MUST have control of the TBB.

# 2.1.2 Transferring Control

Prior to transferring control an executing entity MUST measure the entity to which it will transfer control.

# 2.2 PCR Usage

# Start of informative comment:

This section defines the PCR assignments used for boot time integrity metrics and the methodology for collecting the metrics. The first eight PCRs are defined for use within the Pre-Boot environment (PCR[4] being transition code which is partially Pre-Boot.) Throughout the BIOS boot process a log of all executable code is created and extended into PCRs as described below.

Each time a PCR is extended, a log entry is made in the TCG Event Log. This allows a Challenger to see how the final PCR digests were built.

### End of informative comment..

Summary of the defined PCR usage:

| PCR<br>Index | PCR Usage                                                 |

|--------------|-----------------------------------------------------------|

| 0            | CRTM, BIOS and Platform Extensions                        |

| 1            | Platform Configuration.                                   |

| 2            | Option ROM Code.                                          |

| 3            | Option ROM Configuration and Data.                        |

| 4            | IPL Code (usually the MBR)                                |

| 5            | IPL Code Configuration and Data (for use by the IPL code) |

| 6            | State Transition and Wake Events                          |

| 7            | Reserved for future usage. Do not use.                    |

# 2.2.1 PCR[0] - CRTM, POST BIOS and Embedded Option ROMs

# Start of informative comment:

The CRTM may measure itself to PCR[0] and must measure to PCR[0] any portion of the POST BIOS, including Manufacturer Controlled Embedded Option ROMs, firmware, etc. that are provided as part of the Motherboard. Only executable code is logged. Configuration data such as ESCD should not be measured as part of this PCR.

All these components and any update to them are under the control of the manufacturer or its agent.

If, for any reason, a measurement cannot be made to this PCR none of the following PCR values can be trusted and therefore are outside the chain of trust. It is therefore necessary to invalidate all platform PCRs.

# End of informative comment.

### **Entities that MUST be Measured:**

- The CRTM's version identifier.

- All firmware physically bound to the motherboard

- Manufacturer Controlled Embedded Option ROMs

- These are Embedded Option ROMs whose release and update is controlled by the Manufacturer.

- Embedded SMM code and the code that sets it up.

- ACPI flash data prior to any modifications.

- BIS code (excluding the BIS certificate).

If the measurement of the CRTM, POST BIOS and Embedded Option ROMs cannot be made, the CRTM MUST extend the value 01h to each PCR in the range 0-7.

### **Entities that MAY be Measured:**

Any other code or information that is relevant to the CRTM, POST BIOS or Platform Extensions.

# Method for Measurement for a Compound BIOS:

The CRTM performs these measurements as follows:

- 1. Log the CRTM's version identifier.

- 2. Measure the code to which the CRTM is transferring control.

The POST BIOS may need to reconstruct events that could not be recorded due to the unavailability of memory. If it does so it places this information into the Event Log and MUST NOT extend PCR[0] with this reconstructed information.

3. The remaining measurements MAY be performed in any order.

# Method for Measurement for an Integrated BIOS:

The CRTM performs these measurements as follows:

- 1. Log the CRTM's version identifier.

- 2. The CRTM measures the remainder of the All BIOS firmware.

# 2.2.2 PCR[1] - Motherboard Configuration

# Start of informative comment:

Information about the configuration of the Motherboard including hardware components and how they are configured is measured to PCR[1].

The BIS Certificate may contain information that is privacy sensitive; thus exclusion of the BIS Certificate is allowed.

The method and policy of disabling measurements is manufacturer specified.

### End of informative comment.

These measurements occur only while in the Pre-Boot state.

# **Entities that MUST be Measured:**

The following entities MUST always be measured. These MUST NOT be disabled:

- If the BIOS loads a CPU microcode update, it is measured.

- Platform Configuration including the state of any disable flags affecting the measurement of entities into this PCR.

### **Entities that MAY be Measured:**

The following entities MUST be measured if measurement of the following entities is enabled by the system. These MAY be Disabled:

- BIS certificate.

- POST BIOS-Based ROM strings.

### **Entities that MAY be Measured**

While the code to implement the above entities is mandatory, the code to implement measurement of these entities is optional. It is not required to measure the components of the following that contain privacy information but if implemented, the rest of the information MUST be.

- ESCD, CMOS and other NVRAM data

- SMBIOS structures

- Passwords

# **Entities that MUST NOT be Measured**

- Values and registers that are automatically updated (e.g., clocks).

- System unique information such as asset, serial numbers, etc.

### **Method for Measurement:**

The BIOS performs these measurements as follows:

1. The entities specified in this PCR MAY be measured in any order deemed appropriate by the implementer. Where possible these measurements SHOULD occur prior to measuring Option ROMs.

# 2.2.3 PCR[2] - Option ROM Code

# Start of informative comment:

Option ROMs contained on non-Platform adapters are measured by the BIOS to PCR[2]. There may be two portions of Option ROMs: Visible and Hidden. Each is measured and logged to PCR[2].

# **Visible Portion**

The portion of the Option ROM that is visible to the BIOS MUST be measured by the BIOS.

# **Hidden Option ROM Code**

Some Option ROMs may use paging or other techniques to load and execute code that was not visible to the BIOS when measuring the visible portion of the Option ROM. It is the responsibility of the Option ROM to measure this code prior to executing any portion of that hidden Option ROM code.

### End of informative comment.

Any application that modifies the Option ROM code MUST measure the new code into PCR[2] or cause a Platform Reset.

# **Entities to be Measured:**

- The portion of the Option ROM that is visible to the BIOS.

- The portion of the Option ROM that is not visible to the BIOS is measured by the Option ROM.

- Non-Manufacturer Controlled Embedded Option ROMs

These are Embedded Option ROMs that are physically contained on the Motherboard (as opposed to an add-in card) but the release and control of any update is not controlled by the (Motherboard) Manufacturer.

### **Method for Measurement:**

The BIOS performs these measurements as follows:

- 1. Log the event OptionROMExecute for each option ROM.

- 2. The entities specified in this PCR MAY be measured in any order deemed appropriate by the implementer.

- 3. Repeat until all Option ROMs are measured and executed.

Option ROMs perform these measurements as follows when they execute:

- 1. Measure the event "Un-hiding Option ROM Code" when un-hiding Option ROM code.

- 2. Measure the "hidden" Option ROM Code.

# 2.2.4 PCR[3] – Option ROM Configuration and Data

# Start of informative comment:

As Option ROMs execute, they may have configuration and other data relevant to the trusted properties of the Platform. Option ROMs perform this measurement.

### End of informative comment.

Any application that modifies the Option ROM configuration MUST measure the new configuration into PCR[3] or cause a Platform Reset.

### **Entities to be Measured:**

- Configuration data specific to Option ROM or the adapter that hosts the Option ROM.

- Other data, including comments, specific to Option ROM or the adapter that hosts the Option ROM.

# **Method for Measurement:**

The Option ROM or Application performs these measurements as follows:

1. Measures the event OptionROMConfig.

2. Measure any of the above in any order while executing.

# 2.2.5 PCR[4] - IPL Code

# Start of informative comment:

If IPL code returns control back to the BIOS, each subsequent IPL must be separately measured.

### End of informative comment.

### **Entities to be Measured:**

- Each IPL that is attempted and executed.

- Additional code that is loaded by the IPL.

### **Entities to Exclude:**

Portions of IPL pertaining to the specific configuration of the platform. (e.g., disk geometry in the MBR).

### **Method for Measurement:**

See section 6.2.3 Logging of Boot Events for further detail.

The BIOS performs these steps as follows:

- 1. Measure EV ACTION with the relevant event.

- 2. Measure the IPL Code.

- 3. If control returns to the BIOS, measure that event.

- 4. Go to Step 1.

A complete description of the method for measuring is found in Section 6 IPL Code, Power States, and Transitions

# 2.2.6 PCR[5] - IPL Configuration and Data

### Start of informative comment:

The IPL Code may have configuration or other data that is relevant to the trusted properties of the Platform. An example of this is IPL code that allows the selection of alternate boot partitions. In this example, the partition selection information would be logged to this PCR by the IPL code.

Information measured into this PCR by the BIOS is static information embedded within the IPL code such as the disk geometry within the MBR.

### End of informative comment.

# **Entities to be Measured:**

- All relevant IPL configuration data.

- Static data contained within the IPL Code (e.g., disk geometry)

# **Method for Measurement:**

The IPL code measures all relevant IPL configuration data per its defined events.

The BIOS measures the static data as events defined in Section 7.2.2 Platform Specific Event Log

# 2.2.7 PCR[6] - State Transition

# Start of informative comment:

Events recorded to this PCR are events related to State Transitions and Wake Events.

# End of informative comment.

# **Entities to be Measured:**

- Wake Events

- All relevant State Transitions.

# **Method for Measurement:**

Wake events are measured by the Pre-Boot components as defined in Section 7.2.2 Platform Specific Event Log

State Transitions are measured by the Post-Boot components as defined in Section 7.2.2 Platform Specific Event Log

# 2.2.8 PCR[7] - Reserved

# Start of informative comment:

Reserved to future Pre-Boot use.

# 3. Platform Setup and Configuration

# 3.1 Pre-Boot ROM-based Setup

Upon completion, this setup utility MUST perform a Platform Reset. This includes setup utilities provided by both the motherboard-based BIOS and Option ROMs.

Entry into this state is measured as event "Entering ROM Based Setup".

# 3.2 Post-Boot ROM-based Setup

### Start of informative comment:

This is ROM-based setup accessed via keyboard hot-key during post-boot state.

# End of informative comment.

The setup utility MUST NOT allow changes to platform configuration unless the Post-boot environment can measure the event or the setup utility provides a mechanism to notify the Post-Boot OS that a change occurred.

# 3.3 Reference Partition

This is treated as IPL code. The setup utility within the reference partition MUST measure events that affect platform configuration.

# 3.4 OS Based Setup Utility

The setup utility MUST measure events that affect platform configuration.

# 4. Maintenance

# Start of informative comment:

Maintenance for the PC Specific Implementation Specification refers to the processes surrounding upgrade or replacement of the system BIOS ROM / Flash. All requirements for TPM maintenance are manufacturer defined.

### End of informative comment.

Implementation of Maintenance is optional. If it is implemented it MUST be implemented as defined in this section.

# 4.1 BIOS Recovery Mode

# Start of informative comment:

This is a failure-recovery mode of the BIOS that is invoked by the BIOS Boot Block typically when the main BIOS is corrupt. The BIOS Recovery mode will perform a minimal initialization of the system and then attempt to boot from floppy disk.

A couple of attack scenarios have been identified due to the "BIOS Recovery" feature implemented in many BIOSes. A method to counter these attacks could implement:

- A hardware signal (e.g., GPIO or similar) to "disable" the TPM (until the next TPM\_Init); or,

- Modifications to CRTM recovery code which would extend the value 1 to the pre-Boot PCRs; or,

- Disable the TPM by calling TPM Startup(stTrpe=TPM ST DISABLE)

# End of informative comment.

It MUST NOT be possible for a BIOS Recovery Mode to allow impersonation of another valid boot state. This applies to the values in the pre-Boot PCRs. Upon completion, the BIOS Recovery Code MUST cause a Platform Reset.

# 4.2 Flash Maintenance

### Start of informative comment:

There are two scenarios: An Manufacturer Approved Environment (MAE), and Non-MAE. The MAE may update any portion of the BIOS while the Non-MAE may not update the CRTM.

# End of informative comment.

# 4.2.1 Manufacturer Approved Environment (MAE)

# Start of informative comment:

This is using a utility that is approved by the Manufacturer of the Platform.

# End of informative comment.

The CRTM MAY be updated while in MAE.

# 4.2.2 Non-Manufacturer Approved Environment (NMAE)

# Start of informative comment:

This is using a utility that is not approved by the Manufacturer of the Platform.

# End of informative comment.

The CRTM MAY NOT be updated while in NMAE.

# 5. TCG Credentials

All TCG Credentials MUST be represented as Certificates as defined in Section "9.5 Instantiation of Credentials as Certificates" in the TCPA Main Specification.

# 5.1 Platform Certificate

Distribution is manufacturer controlled.

# 5.2 Platform Conformance Certificate

Distribution is manufacturer controlled.

# 5.3 Method of Verification

Verification of the entity against the hash value within the Validation Certificate is not required. If performed, the hash within the Validation Certificate must include the entire Validation Certificate Header excluding the Validation Certificate itself.

# 5.4 Validation Certificate Header

If present, the Validation Certificate will be contained within the Option ROM header as specified below according to the "Plug and Play BIOS Specification".

| Offset | Size   | Value              | Description                                                                                                                      |  |

|--------|--------|--------------------|----------------------------------------------------------------------------------------------------------------------------------|--|

| 0h     | DWORD  | 41h, 50h, 43h, 54h | This is the byte sequence 41h, 50h, 43h, 54h which is the ASCII string 'TCPA' for compatibility with the original specification. |  |

| 04h    | BYTE   | 01h                | Structure Revision                                                                                                               |  |

| 05h    | BYTE   | Varies             | Length (in 16 byte increments)                                                                                                   |  |

| 06h    | WORD   | Varies             | Offset of next Header (0000 if none)                                                                                             |  |

|        | BYTE   | Varies             | Number of segments. Value of 0 indicates entire visible portion of Option ROM excluding the Validation Certificate               |  |

|        | WORD   | Varies             | Offset to 1 <sup>st</sup> segment included in Validation Certificate hash                                                        |  |

|        | WORD   | Varies             | Length-1 of 1 <sup>st</sup> segment included in Validation Certificate hash                                                      |  |

|        |        |                    | Repeat for number of segments.                                                                                                   |  |

|        |        |                    |                                                                                                                                  |  |

| ??h    | BYTE   | 0FFh               | Reserved                                                                                                                         |  |

| ??h    | BYTE   | Varies             | Checksum of this entire header as specified in the Plug and Play BIOS Specification                                              |  |

| ??h    | Varies | Varies             | Validation Certificate                                                                                                           |  |

# 6. IPL Code, Power States, and Transitions

# 6.1 Architecture and Definitions

### Start of informative comment:

A handoff to an operating system generally occurs after BIOS has completed its initialization and testing of the platform hardware. BIOS searches through predefined sequence of boot devices looking for an operating system. TCG-enabled BIOS will load an IPL, check for boot ability, and just before jumping to the MBR, perform a hash on the code contained within the first 512 bytes where the master boot record is located. This hash will then be extended into PCR[4]. In general, any code that is loaded and jumped to from the BIOS must be hashed and extended into PCR[4] prior to turning control of the system over to that code. The BIOS MUST not hash any data areas.

There can be a number of entries in the boot sequence, but until a bootable device is found, the MBR is not hashed. Just before jumping to the operating system and after the MBR has been loaded into memory, this code must be hashed and extended into PCR[4]. If the operating system returns back to the BIOS through an INT 18h call, then the next boot device is checked for boot ability and the process repeats. The important thing to remember is that each time PCR[4] is extended, an entry is added to the log.

Another item of concern during this phase of a TCG-enabled platform is the passing of the root of trust. The BIOS will pass the chain of trust to the MBR and it is up to the MBR to preserve the chain of trust and pass it to the OS.

End of informative comment.

# 6.2 Procedure for Transitioning the TPM from Pre-Boot to Post-Boot

# Start of informative comment:

In order to transition from the Pre-Boot state to the Post-Boot state in a TCG protected environment, a number of steps need to be performed. This section of the specification will outline and describe these steps.

End of informative comment.

# 6.2.1 Extending PCR[4] - The IPL Code

# Start of informative comment:

Just before handing control over to the operating system, the BIOS needs to perform several actions in order to assure that trust in the platform has been maintained. One of the important events that need to occur is the extending of PCR[4]. This is done utilizing the BIOS function INT 1Ah where AH = BBh and AL = 01h (HashLogExtendEvent) to hash the first 512 bytes of the boot device.

End of informative comment.

# 6.2.2 Extending PCR[5] – IPL Configuration and Data

### Start of informative comment:

PCR[5] is reserved for any configuration data that various transition code may need. For example, if a BIOS is transitioning to a MBR on a hard drive, then there may be no configuration needed. However, this PCR is to be utilized and extended by any boot loader for variable data.

# 6.2.3 Logging of Boot Events

### Start of informative comment:

A log is provided in memory for the eventual challenger to make a determination of the state of trust of the platform. The OS handoff code needs to fill this log with information about the boot devices used to get to an operating system. The BIOS functions designed for hashing and extending the various PCRs should automatically log the extending events.

While the extending of the PCRs is an automatic process in regards to logging, there are other events and information that this specification will require. The following is a list of common log entries that should be recorded prior to turning over control of the system.

- The type of device that was booted to and specific information about this device, which can uniquely identify it within the system.

- Each attempt to a boot device should measure:

- An EV\_SEPARATOR event to all pre-boot PCR (0-7) to delimit pre-boot and postboot events

- The boot device attempted

- Any time a boot device returns back to the BIOS through INT 18h should be logged as an

event.

### End of informative comment.

Prior to calling Int19h, the event EV\_SEPARATOR SHALL be measured to the pre-boot PCRs (PCR[0-7]). This SHALL be followed by measuring the event "Calling INT 19h" to PCR[4]. If a boot device returns, an event indicating the nature of the return SHALL be measured to PCR[4]. Subsequent attempts to boot SHALL measure the boot device to PCR[4] and the event EV SEPARATOR to the pre-boot PCRs (PCR[0-7]).

# 6.2.4 Passing Control of the TPM from Pre-Boot to Post-Boot

### Start of informative comment:

Once the BIOS has turned control over to an operating system, the Post-Boot environment will load its own set of drivers and code to access the TPM. This could cause a potential conflict since there may be contention between the Post-Boot and the Pre-Boot environments for use and access of the TPM.

The INT 1Ah interface provides for a solution to this problem through function TCG\_ShutdownPreBootInterface. Once the Post-Boot environment has loaded its driver support, it MAY call this function to disable the BIOS support. Such a handoff procedure allows for the BIOS support to remain on non-TCG aware operating systems and removes the contention of the TPM hardware on TCG aware operating systems.

# End of informative comment.

# 6.2.5 Various Boot Devices and Special Treatment they may receive

# Start of informative comment:

BIOS Aware IPL Devices (BAID):

These are devices such as floppy drives, hard drives, CD-ROM drives, etc. The IPL code of these devices will be measured in PCR[4] just before jumping to this code.

Legacy IPL Devices

Option ROMs will have already been measured. INT 18h and INT 19h events will be measured as events per Section 7.2.3 EV\_ACTION. It is the Option ROM's responsibility to measure any additional code loaded.

### PNP Cards

# Boot Connection Vector (BCV)

These include devices such as PnP SCSI cards w/ drive and Non-PnP card w/ expansion header. These cards generally require two BIOS calls, one to return their capabilities and another call to have them hook INT 13h. For the case of the cards that have an associated local mass storage device (SCSI cards with a bootable hard drive), then the BIOS MUST measure the code portion of the first 512 bytes of the mass storage device into PCR[4].

# Bootstrap Entry Vector (BEV)

A device (generally a network card) that uses a BEV for booting will require that it is called through INT 19h. The Option ROM will need to measure the initial IPL image obtained from the network to PCR[4] prior to jumping to this code.

### PARTIES Partition

The PARTIES Partition is a hidden partition on the hard drive that BIOS can use for additional storage space and as a virtual drive. In the PARTIES Partition there is a small section called the BEER. Prior to turning control over to the PARTIES Partition, the BIOS must measure the BEER area into PCR[5].

The partition that is booted to in the PARTIES Partition must also have the initial IPL image code measured into PCR[4] prior to turning control over to this code.

### El Torito

When the BIOS boots to a CDROM device that supports the EI Torito specification, it first loads the Booting Catalog. If there is more then one boot image on the CD, the user is then prompted to select the boot image. Using this selection and the Booting Catalog, the BIOS loads the first 512 bytes of the CDROM that contains the image into memory and turns control over to this code. Prior to jumping to this code, the BIOS MUST measure the initial IPL image of the boot image code into PCR[4]. The BIOS code will also measure the entire contents of the boot catalog into PCR[5]. The measurement of the boot catalog will be done prior to the measurement of the initial IPL image.

# Legacy Reboot

Software can store a jump vector in the BDA, set a bit in CMOS, then Platform Reset the system so that the jump vector will be executed as a boot device. Since this code has already been measured no further measurement is required.

# End of informative comment.

# 6.3 Power States, Transitions, and TPM Initialization

### Start of informative comment:

Suspend is designed to reduce overall power consumption under software control. For instance, Windows 2000 or Linux support a power management standard called ACPI (Advanced Control Power Interface Specification). This standard defines a set of power states that can change the behavior of a device during sleeping states.

# 6.3.1 Definitions and Conditions during Power States

### Start of informative comment:

These are the Sx states as defined in the ACPI specification. The only transitions allowed are those defined in the ACPI definitions.

Platforms and Post-BIOS Operating Systems MUST support ACPI.

End of informative comment.

# 6.3.1.1 S1: Stand-by - Low wakeup latency sleeping state

**TPM State:** Fully working, because the TPM is still under power during S1 sleep state.

Entering S1: Nothing to do.

During S1: Nothing to do.

Exiting S1: Nothing to do.

# 6.3.1.2 S2: Stand-by with CPU context lost

**TPM State:** Fully working, because the TPM is still under power during S2 sleep state.

Entering S2: Nothing to do.During S2: Nothing to do.Exiting S2: Nothing to do.

# 6.3.1.3 S3: Suspend To Ram

**TPM State:** S3 is the most complex mode to handle, because PCR values are to be preserved by

the platform during this mode. The mechanism to preserve the values cannot be accessible outside the TPM. During S3 the TPM must prohibit all TPM functions.

**Entering S3:** The post-boot driver MAY issue the TPM SaveState.

**During S3:** May have power. This is hardware design dependent. If the TPM has the ability to

preserve the contents of the PCRs without power, no power is needed to the TPM. However, if the TPM cannot maintain the contents of the PCRs without power, the Motherboard MUST provide sufficient power to the TPM to maintain the PCRs.

**Exiting S3:** The command to restore the PCRs is issued by the CRTM.

# 6.3.1.4 S4 OS: Suspend To Disk

**TPM State:** All power, including auxiliary, is removed.

**Entering S4:** Nothing to do.

**During S4**: The TPM is off – Nothing to do.

Exiting S4: The PCRs will be lost, including the PCRs used by the OS, therefore the OS must

establish new integrity. The OS, therefore, cannot attest to its original power-on state.

# 6.3.1.5 S4 BIOS: Suspend To Disk

**TPM State:** All power, including auxiliary, is removed.

Version 1.1 Aug 13, 2003

Entering S4: Nothing to do.

**During S4**: The TPM is off – Nothing to do.

**Exiting S4**: The PCRs will be lost, including the PCRs used by the OS, therefore the OS must

establish new integrity. The PCR contents may be different from S4 from OS.

# 6.3.1.6 S5: Off State

**TPM State:** All power, including auxiliary, is removed.

Entering S5: Nothing to do.

**During S5**: The TPM is off – Nothing to do.

Exiting S5: The PCRs will be lost, including the PCRs used by the OS, therefore the OS must

establish new integrity.

# 6.3.2 Power State Transitions

# Start of informative comment:

Each section below describes the behavior and process between the various power states.

# End of informative comment.

In the following pseudo code is a suggested set of implementation that generalized the control flow of the motherboard during the pre-Boot state. Not all conditions and error states are included. This intended only as a guide.

# 6.3.2.1 S5 $\rightarrow$ S0

### Start of informative comment:

This the transition from a power-off state to a power-on state. Platform Reset is asserted. The full BIOS initialization sequence is executed.

### End of informative comment.

Starting from a power off state.

```

Disable the platform

}

if (Normal boot)

MAHashAllExtendTPM(Initial POST BIOS, PCR[0])

GoTo POST BIOS // Transfer control to POST BIOS

// Note: the following else cluase is optional depending if either the

// BIOS Recovery Mode or a Utility requiring physical presence

// indication from the boot state is part of the motherboard's design.

else if (executing BIOS Recovery Mode)

MAHashAllExtendTPM(BIOS Recovery Code, PCR[0])

GoTo BIOS Recovery Code

else if (indication of physical presence given to BIOS)

if (Platform requires physical presence during

boot state)

{

MAHashAllExtendTPM(Utility, PCR[0])

MAPhysicalPresenceTPM( TPM PC PHYSICAL PRESENCE MASK SW |

TPM PC PHYSICAL PRESENCE PRESENT)

GoTo Physical Presence Utility

}

}

POST BIOS:

TCG StatusCheck()

Optionally TCG PassThroughToTPM(TPM DisableOwnerClear)

Optionally TCG PassThroughToTPM(TPM DisableForceClear)

If (Embedded Option ROMs)

TPMHashAllExtendCRTM(Embedded Option ROMs, PCR[0])

TCG HashLogExtendEvent(Platform Configuration, PCR[1])

While (Unexecuted Option ROM present)

TCG HashLogExtendEvent(Visible Portion of Option ROM, PCR[2])

Transfer control to Option ROM.

INT 18:

Choose next IPL Code

TPMHashAllExtendCRTM(PCR[4], Chosen IPL Code)

TPMHashAllExtendCRTM(PCR[0-7], EV_Separator)

TPMHashAllExtendCRTM(PCR[4], "Calling INT 19h")

INT 19h // To Execute IPL Code

IPL:

TCG HashLogExtendEvent(IPL Configuration Data, PCR[5])

Transfer Control to OS Loader

if (OS loader fails to load OS)

GoTo INT 18

```

### BIOS Recovery Code:

Transfer control of platform to BIOS Recovery Code When complete perform Platform Reset

# Physical Presence Utility:

Transfer control of platform to Utility Requiring Physical Presence When complete perform Platform Reset

END

### 6.3.2.2 S1 $\rightarrow$ S0

### Start of informative comment:

Resume from an S1 suspend state. Platform Reset has never been asserted so the TPMInitCRTM function cannot be called. CRTM executes code to perform resume without re-measuring Pre-Boot components. CRTM passes control directly to the OS. If there are any changes to the Platform's components or configuration, measuring these changes is the responsibility of the OS.

## End of informative comment.

No Action

# 6.3.2.3 S2 $\rightarrow$ S0

### Start of informative comment:

Resume from an S2 suspend state. Platform Reset has never been asserted so the TPMInitCRTM function cannot be called. CRTM executes code to perform resume without re-measuring Pre-Boot components. CRTM passes control directly to the OS. If there are any changes to the Platform's components or configuration, measuring these changes is the responsibility of the OS.

# End of informative comment.

No Action

# 6.3.2.4 S3 $\rightarrow$ S0

### Start of informative comment:

Resume from an S3 suspend state. Platform Reset is asserted. CRTM executes code to perform resume without re-measuring Pre-Boot components. CRTM passes control directly to the OS. If there are any changes to the Platform's components or configuration, measuring these changes is the responsibility of the OS.

The OS must assure prior to entering S3 that the TPM as preserved the required values.

There must be a countermeasure in the event POST is modified by malicious code and the platform resumes from S3 executing that code. After modifying BIOS, the OS is required to transition the platform to S5 before allowing a transition to S3. This is to allow the new BIOS to be measured. The CRTM is responsible for enforcing this behavior.

# End of informative comment.

CRTM MUST be able to determine if there has been an update to any portion of the BIOS since the previous transition from S5. If the CRTM detects a modification to BIOS since the last transition from S5, the CRTM MUST either:

- Force the platform to transition to S5, or

- Make the contents of PCR[0] invalid.

```

MAInitTPM (stType = TPM_ST_STATE)

If MAInitTPM returned OK

{

If BIOS modified since last S5

{

Force transition to S5.

or

Invalidate PCR[0].

}

Transfer control to the OS.

}

else

{

Force transition to S5.

GoTo MAInitError in 6.3.2.1 S5 → S0

```

# 6.3.2.5 S4 $\rightarrow$ S0

# Start of informative comment:

This is where the IPL instead of loading the OS loader will load memory form a hard disk. Platform Reset is asserted. The full BIOS initialization sequence is executed just like the S5->S0 transition. If there are any changes to the Platform's components or configuration, measuring these changes is the responsibility of both the Pre-Boot and the Post-Boot states.

# End of informative comment.

Same as S5->S0 except IPL loads the saved memory image.

# 7. Event Logging

# 7.1 ACPI Table Usage

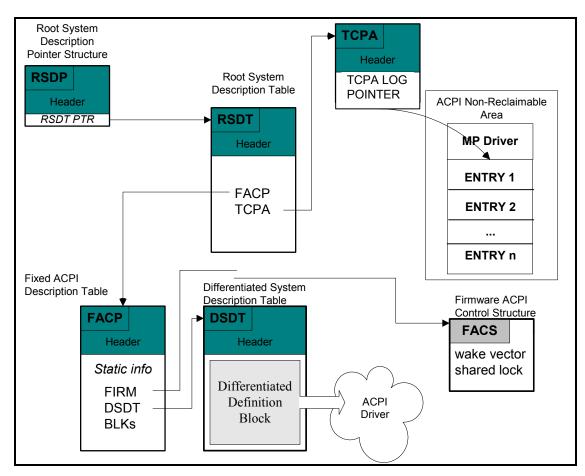

# Start of informative comment:

A system's firmware uses an ACPI table to identify the system's TCG capabilities to the Post-Boot environment. The information in this table is not guaranteed to be valid until the BIOS performs the transition from pre-boot state to post-boot state.

The firmware "pins" the memory associated with the pre-boot TCG log, and reports this memory as "Reserved" memory via the IA32 INT 15h/E820 interface. This is done to ensure that the log area contains the EXTEND operations performed on the most recent system transition from S5 or S4. If the log were in reclaimable memory, the firmware would not be able to report the system configuration on the return from hibernation (S4) since the memory would have been reclaimed for other use by the operating system on its last boot from S5.

Note: The character string 'TCPA' is used for compatibility with previously defined structures.

# End of informative comment.

■ Figure 7-1 ACPI Structure

| Field                             | Byte<br>Length | Byte<br>Offset                              | Description                                                                                                                      |

|-----------------------------------|----------------|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Header                            |                |                                             |                                                                                                                                  |

| Signature                         | 4              | 0                                           | This is the byte sequence 41h, 50h, 43h, 54h which is the ASCII string 'TCPA' for compatibility with the original specification. |

| Length                            | 4              | 4                                           | Length, in bytes, of the entire TCG Table. The length implies the number of Entry fields at the end of the table.                |

| Revision                          | 1              | 8                                           | 1                                                                                                                                |

| Checksum                          | 1              | 9                                           | Entire table must sum to zero.                                                                                                   |

| OEMID                             | 6              | 10                                          | For instance: "HPINVT"                                                                                                           |

| OEM Table ID                      | 8              | 16                                          | For the TCG Table, the table ID is the manufacture model ID.                                                                     |

| OEM Revision                      | 4              | 24                                          | OEM revision of TCG table for supplied OEM Table ID.                                                                             |

|                                   |                | 28                                          | Vendor ID of utility that created the table.                                                                                     |

|                                   |                | Revision of utility that created the table. |                                                                                                                                  |

| Reserved                          | 2              | 36                                          | Reserved for future assignment by this specification, set to 0000h.                                                              |

| Log Area Maximum<br>Length (LAML) | 4              | 00                                          | Identifies the maximum length (in bytes) of the system's pre-boot TCG event log area.                                            |

| 4                                 |                | 38                                          | <b>Note</b> : For TCG 1.1b, this maximum log size is 64KB.                                                                       |

| Log Area Start<br>Address (LASA)  | 8              | 42                                          | Contains the 64-bit physical address of the start of the system's pre-boot TCG event log area, in QWORD format.                  |

|                                   |                |                                             | <b>Note</b> : The log area ranges from address LASA to LASA+(LAML-1).                                                            |

# 7.2 Measurement Event Log

# Start of informative comment:

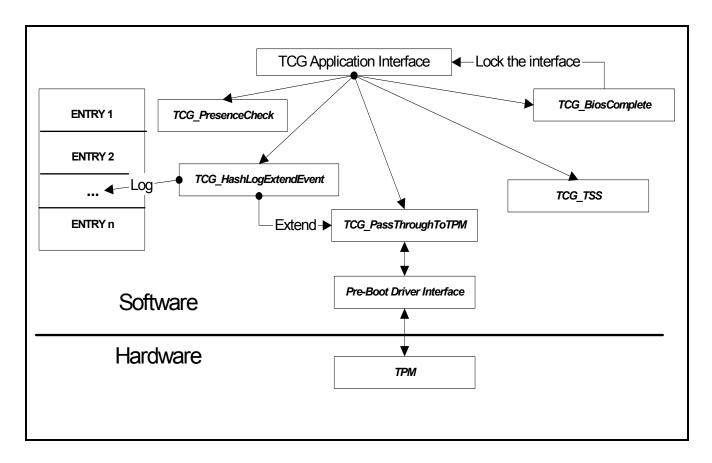

# TCG\_HashLogExtendEvent

Events are logged using the TSS\_PCR\_EVENT structure which is defined and documented in the TCG TSS Specification These structures are stored as an unstructured array within the ACPI data area as defined in Section 7.1 ACPI Table Usage. None of the pre-Boot entities, including ACPI, are required to interpret this data. The storage of this data using ACPI is a convenience because there are defined mechanisms already in place to allow the transfer of this information to the Post-Boot State. Once the Post-Boot State controls the platform, the Post-Boot OS is expected to read this data and transfer it to its own event log.

# End of informative comment.

The instantiation of the event log is an array of TSS\_PCR\_EVENT structures as defined below.

# 7.2.1 Platform Independent Event Log Structure

Platform independent events SHALL be done using the events identified in the TCPA Main Specification. Examples of these are Validation Certificates. These are logged using the EV\_CODE\_CERT event type.

# 7.2.2 Platform Specific Event Log

For the events described in this section the EventType SHALL be EV\_PLATFORM\_SPECIFIC and the event field within the TSS\_PCR\_EVENT structure SHALL be the PlatformSpecificEventLogStruct as defined in Section 7.2.2.1 Platform Specific Event Log Structure.

# 7.2.2.1 Platform Specific Event Log Structure

The Events shall be the following structure.

```

PlatformSpecificEventLogStruct STRUCT

EventID DD ? / Tag as defined in

Section 7.2.2.2 Platform Specific Event Tags

EventDataSize DD ? / Size of EventData

EventData DB ? / EventData

PlatformSpecificEventLogStruct ENDS

```

# 7.2.2.2 Platform Specific Event Tags

The EventID and EventDataSize elements are represented in big endian format.

# 7.2.2.2.1 SMBIOS structure

Each event MAY consist of one or more complete SMBIOS records. This event may appear multiple times in the event log. The SMBIOS structure SHALL be logged using the following:

```

EventID = 0001h

```

EventData[] = One or more raw complete SMBIOS records.

# 7.2.2.2.2 BIS Certificate

The BIS Certificate SHALL be logged using the following:

```

EventID = 0002h

```

EventData[] = Raw BIS Certificate

# 7.2.2.2.3 POST BIOS ROM Strings

The BIOS ROM Strings SHALL be logged using the following:

```

EventID = 0003h

```

EventData[] = Hash of POST BIOS ROM Strings

# 7.2.2.2.4 ESCD

The ESCD SHALL be logged using the following:

EventID = 0004h

EventData[] = Hash of ESCD Data

# 7.2.2.2.5 CMOS

The CMOS SHALL be logged using the following:

EventID = 0005h

EventData[] = Raw CMOS Data

# 7.2.2.2.6 NVRAM

The NVRAM SHALL be logged using the following:

EventID = 0006h

EventData[] = Raw NVRAM contents

# 7.2.2.2.7 Option ROM Execute

The BIOS logs the execution of each Option ROM into PCR[2] using the following:

EventID = 0007h

EventData[] = OptionROMExecuteStructure(including the PFA)

# 7.2.2.2.8 Option ROM Configuration

Option ROMs log events into PCR[3] using the following:

EventID = 0008h

Event[] = OptionROMConfigStructure( include PFA)

# 7.2.2.2.9 Option ROM Microcode Update

Option ROMs log events into PCR[2] using the following:

EventID = 000Ah

Event[] = Hash of Microcode that will be loaded.

# 7.2.3 EV\_ACTION Event Types

The following actions strings are defined. The strings below are enclosed in quotes for clarity; the actual log entries SHALL not include the quote characters. They SHALL be logged using the following:

EventType = EV\_ACTION

Event[] = ASCII string of the following:

| String                           | Purpose and Comments                                                                                                                                                                                        | PCR |

|----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| "Calling INT 19h"                | BIOS is calling INT 19h. If no additional strings posted in log that means that the software which 'hooked' the INT 19 vector did not return control to the BIOS.                                           | 4   |

| "Returned INT 19h"               | BIOS Received control back from prior INT19h invocation.                                                                                                                                                    | 4   |

|                                  | If the called code is not TCG-aware it may have loaded additional unmeasured code. However there is a log entry showing entry to (and measurement of) untrusted code.                                       |     |

| "Return via INT 18h"             | BIOS Received control back via INT 18h                                                                                                                                                                      | 4   |

|                                  | If the called code is not TCG-aware it may have loaded additional unmeasured code. However there is a log entry showing entry to (and measurement of) untrusted code.                                       |     |

| "Booting BCV Device s"           | BIOS is IPL/Booting a BCV Device.                                                                                                                                                                           | 4   |

|                                  | The value 's' is a ASCII string that unambiguous describes the boot device. This SHOULD include an indication of logical or physical device location and any ID string returned by the device.              |     |

| "Booting BEV Device s"           | BIOS is IPL/Booting a BEV Device.                                                                                                                                                                           | 4   |

|                                  | The value 's' is an ASCII string supplied by the BEV device.                                                                                                                                                |     |

| "Entering ROM Based Setup"       | BIOS is entering ROM based Setup during preboot environment.                                                                                                                                                | 0   |

| "Booting to Parties N"           | BIOS is IPL/Booting from a Parties Partition #N.                                                                                                                                                            | 4   |

|                                  | The value n is the actual numeric value of the partition number represented as a printable ASCII hex value. (e.g. partition zero would get the string value "0"). Where N is the index into the BEER table. |     |

| "User Password Entered"          | User has entered the correct user password.                                                                                                                                                                 | 4   |

| "Administrator Password Entered" | User has entered the correct administrator password.                                                                                                                                                        | 4   |

| "Password Failure"               | The typed password did not match the stored password after a specified number of retries.                                                                                                                   | 4   |

# Page 37

| "Wake Event n"                                         | Cause of the power to be applied to the platform where n is the WfM wake source (e.g. wake source zero would get the string value "0"). | 1 |

|--------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------|---|

| "Boot Sequence User<br>Intervention"                   | User altered the boot sequence                                                                                                          |   |

| "Chassis Intrusion"                                    | The case was opened.                                                                                                                    | 1 |

| "Non Fatal Error"                                      | A non-fatal POST error (e.g. keyboard failure) was encountered. This is any error that allows the system to continue the boot process   | 1 |

| "Start Option ROM Scan"                                | BIOS has started the Option ROM scan.                                                                                                   | 2 |

| "Unhiding Option ROM Code"                             | Unhiding Option ROM Code                                                                                                                | 2 |

| " <oprom non-ipl<br="" specific="">String&gt;"</oprom> | An Option ROM vendor specific string for non-Boot/IPL events.                                                                           | 3 |

| " <oprom ipl="" specific="" string="">"</oprom>        | An Option ROM vendor specific string for Boot/IPL events.                                                                               | 5 |